各大公司竞相将各种芯片架构作为将AI推向边缘的首选武器。

随着机器学习应用开始出现在终端设备和物联网网络边缘,实现AI的加速器可能看起来更像FPGA和SoC模组,而不是英特尔和英伟达目前的数据中心绑定芯片(data-center-bound chip)。

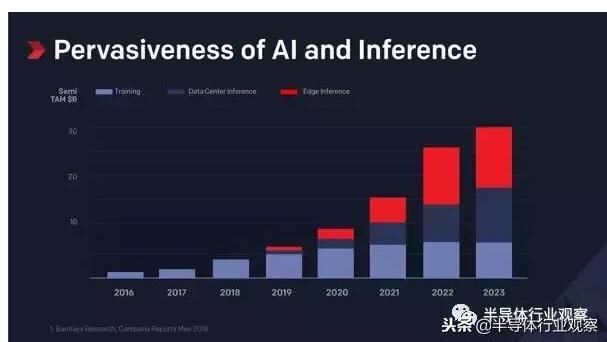

人工智能和机器学习需要功能强大的芯片来从大数据集中计算答案。大多数AI芯片——包括训练和推理——都是为数据中心开发的。然而,这种趋势很快就会改变。其中很大一部分处理将发生在边缘,即网络的边缘或传感器和传感器阵列的内部或附近。

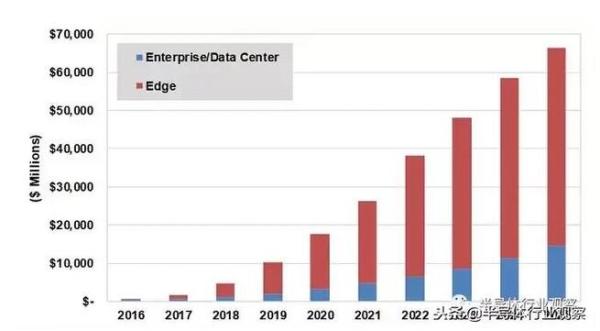

几乎可以肯定,训练将留在云端,因为对于这一大块资源的最有效产品是英伟达的GPU,它主导着这一部分市场。尽管数据中心可能会承担包含大量数据集的训练部分,但推理可能最终会交给边缘。市场预测似乎同意这一点。

Tractica公司研究主管、边缘设备AI报告的作者Aditya Kaul说:“推理硬件市场是一个新市场,但变化迅速。数据中心有一些机会,并将继续存在。基于云的数据中心AI芯片市场将继续增长。但是推理处于边缘,这里开始变得引人注目。至少有70家专业人工智能公司正在研究某种与芯片相关的人工智能技术。”

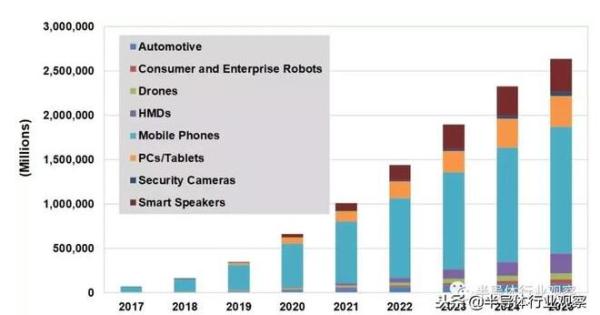

Kaul说:“在边缘,智能手机、机器人、无人机、相机、安全摄像头等所有需要AI处理的设备都将成为未来的热点。”

到2025年,基于云的AI芯片组将带来146亿美元的收入,而基于边缘的AI芯片组将带来516亿美元的收入,是数据中心的3.5倍,边缘AI芯片组主要由手机、智能音箱、无人机、AR/VR耳机,以及其他所有需要AI处理的设备组成。

虽然英伟达和英特尔现在可能主导基于数据中心的机器学习应用的市场,谁将占据远离数据中心的边缘计算AI市场?那些芯片会是什么样子?

AI边缘芯片需要做什么

根据Semico Research公司ASIC和SoC分析师Rich Wawrzyniak所言,边缘计算、物联网和消费终端设备将需要以相对较低的功耗、价格和较小芯片尺寸进行高性能推理处理。这很困难,特别是因为边缘设备处理的大多数数据是庞大的视频和音频数据。

Wawrzyniak说:“数据很多,但如果你有监控摄像头,它必须能够实时识别出坏人,而不是把一张照片发送到云端,然后等着看有没有人认出他。”

将ML级别的智能添加到边缘设备的一些愿望来自于需要将这些设备上的数据保密,或者降低将数据发送到云端的成本。然而,大部分需求来自那些希望设备位于边缘计算设施或掌握在客户手中的客户,他们不希望设备简单地收集数据并定期将其发送到云端,以便他们可以直接与公司自己的数据或其他客户和路人进行实时交互。

NXP半导体AI技术主管Markus Levy表示:“客户意识到,他们不想把大量处理工作转移到云端,因此他们认为边缘是真正的目标。既然你可以在边缘实现AI,你就可以把物联网变成真正具有能力的东西。我们看到消费者物联网、工业物联网以及嵌入式的增长非常快,这是我们最大的增长领域。”

据IDC分析师Shane Rau称,今年接受IDC调查的商业技术客户表示,他们确定会把机器学习转移到边缘设备上,主要是汽车、智能家居、视频监控摄像头和智能手机。该公司的客户调查将这四种设备列为ML的候选设备。

边缘AI架构发展趋势

边缘计算的需求范围可能包括数亿计的工业和消费设备,因此任何单一的架构都不太可能满足所有这些需求。

NXP的Levy表示:在微控制器和相对低端的芯片上运行推理模型是可以的,但大多数机器学习功能需要从基于FPGA、ASIC和其他SoC配置的一长串可选CPU附加项,以及GPU和CPU的组合,有时还需要由Google的TPU等特殊用途的ASIC来增强。

大部分的增强都是以加速器的形式出现的。这些FPGA、SoC、ASIC和其他专用芯片旨在帮助资源受限的基于x86的设备通过一层接一层的分析标准处理大量图像或音频数据,因此app可以正确地计算和加权每个数据的值。

英特尔和英伟达已经向边缘AI市场发起冲击。Kaul说,像英伟达的Jetson这样的产品并不能令人信服。Jetson是一个GPU模块平台,具有7.5W的功率预算,只有英伟达更典型产品的70W功率的一小部分,但对于一般不超过5W的边缘应用来说还是太高了。

Levy说:“有很多IP公司正在为神经网络寻求加速,因此有足够的选择使加速器开始成为边缘设备推理的需求。”

但是,要想在潜在的亿万个设备上添加ML加速和支持,将需要更多的可定制性、更低的成本,以及更专门针对资源受限设备上ML应用需求的规范——这意味着,如果要取得成功,整个市场将需要更好的处理器。

神经推理需要数万亿次乘法累加运算,因为模型从其公式矩阵的一层提取数据,尽管每一层可能需要不同的数据大小,而且其中一些设备可能在输入设置为8位整数而不是16位整数时运行得更快。

Flex Logix联合创始人兼首席执行官Geoff Tate表示:“为了在数据中心获得良好的吞吐量,大多数架构依赖于必须使用相同的权重集来创建批处理的数十或数百个任务。如果你有28张图片,你加载图片,加载第一阶段的权重,对第一阶段做数学运算,保存结果,然后加载第二阶段的权重。通过在每一层上完成所有28个批次,你可以将权重加载时间缩减到一次只加载一个的1/28。如果加载和管理权重是你不擅长的,那么你可以通过批处理来解决它。这就是为什么你会看到基准测试显示第28批的运行效率低于第1批。如果加载权重的速度很慢,则难以扩展。但在数据中心之外的任何地方都必须这样做。如果你有监控摄像头,则必须在图像传入时对其进行处理,以便批大小始终等于1。如果你在测量性能,则数据中心外的批大小始终等于1。”

Flex Logix开发的神经网络引擎可以避免批处理问题。Tate说:“因为我们加载权重的速度非常快,所以我们不需要进行批处理,我们的性能在第1批和第28批时相同,这在边缘应用中非常重要。”

推理硬件方面的两项新工作

Xilinx试图利用其在FPGA和系统级设计方面的经验,推出新的产品系列和路线图,以满足尽可能多的边缘/设备市场的需求。

Xilinx在去年春天讨论了这个想法,但直到10月才正式宣布,该公司描述了一个自适应计算加速平台,该平台“利用CPU、GPU和FPGA的力量来加速一切应用”。

Xilinx的演示描述了一个广泛的产品线、使用案例列表和有关其AI引擎核心的详细信息,其目标是提供比传统方法的单位芯片面积高出3~8倍的性能,并提供高性能DSP能力。

与此同时,Flex Logix创建了一个使用低DRAM带宽的可重构神经加速器。芯片的面积和功率的目标规格将在明年上半年完成,并在下半年流片。推理引擎将充当CPU,而不仅仅是一个更大,更漂亮的加速器。它提供了模块化、可扩展的架构,旨在通过减少移动数据的需要以及通过改进数据和矩阵计算的加载方式来减少瓶颈,从而降低移动数据的时间和精力成本。

该芯片将DRAM专用于单个处理器块,而不是将其作为一个大内存池进行管理。DRAM不能同时将数据馈送到芯片的多个部分。Tate说:“将DRAM作为流入一个处理器块的大内存池处理,这是范诺依曼架构的典型特征,但它不会成为神经网络的成功架构。”